|

NORゲート

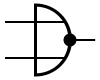

NORゲート(ノアゲート)は否定論理和の論理ゲートであり、その(論理的な)動作は、否定論理和すなわち、全ての入力の論理和(OR)をとったものの反転(NOT)である。つまり、全ての入力がLowの場合のみ出力がHighになり、Highの入力がひとつでもある場合はLowを出力する。 NANDゲート(否定論理積)と同様 functional complete である(詳細は否定論理積#完全性を参照)。 記号MIL論理記号及びANSI、IEC、DINのそれぞれにおけるNORの記法を以下に示す。

ハードウェアの解説とピン配置 NORは、汎用ロジックICではNANDに次ぐ基本的な製品として、バリエーション等が最も豊富な一群のひとつである。74シリーズについてはTTLの7402等の他、74HC02他のCMOS版など多数のバリエーションがある。

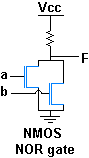

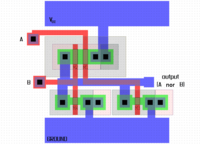

さらに古いRTLやECLといった方式ではNORゲートは効率がよかったため多用されていた。 実装下の左端の図はNMOSで2入力NORゲートを構成した例である。入力のどちらかでもHIGHになれば、対応するMOSFETがONになり、出力をLOWにする。そうでない場合はプルアップ抵抗で出力をHIGHに保っている。下の右端の図はCMOSテクノロジーによる2入力NORゲートの回路図である。入力に付加されているダイオードと抵抗器はCMOS部品を静電放電から守るためのもので、論理的には何の機能もない。

代替実装NORゲートが入手できない場合、NANDゲートを使って下の図のようにNORゲートを構成できる。NANDゲートやNORゲートは、どちらもそれだけで任意の論理ゲートを構成可能である。

関連項目 |

|||||||||||||||||||||||||||||

Index:

pl ar de en es fr it arz nl ja pt ceb sv uk vi war zh ru af ast az bg zh-min-nan bn be ca cs cy da et el eo eu fa gl ko hi hr id he ka la lv lt hu mk ms min no nn ce uz kk ro simple sk sl sr sh fi ta tt th tg azb tr ur zh-yue hy my ace als am an hyw ban bjn map-bms ba be-tarask bcl bpy bar bs br cv nv eml hif fo fy ga gd gu hak ha hsb io ig ilo ia ie os is jv kn ht ku ckb ky mrj lb lij li lmo mai mg ml zh-classical mr xmf mzn cdo mn nap new ne frr oc mhr or as pa pnb ps pms nds crh qu sa sah sco sq scn si sd szl su sw tl shn te bug vec vo wa wuu yi yo diq bat-smg zu lad kbd ang smn ab roa-rup frp arc gn av ay bh bi bo bxr cbk-zam co za dag ary se pdc dv dsb myv ext fur gv gag inh ki glk gan guw xal haw rw kbp pam csb kw km kv koi kg gom ks gcr lo lbe ltg lez nia ln jbo lg mt mi tw mwl mdf mnw nqo fj nah na nds-nl nrm nov om pi pag pap pfl pcd krc kaa ksh rm rue sm sat sc trv stq nso sn cu so srn kab roa-tara tet tpi to chr tum tk tyv udm ug vep fiu-vro vls wo xh zea ty ak bm ch ny ee ff got iu ik kl mad cr pih ami pwn pnt dz rmy rn sg st tn ss ti din chy ts kcg ve

Portal di Ensiklopedia Dunia