|

时序逻辑电路在数字电路理論中,时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成的状态有关。這跟組合邏輯電路相反,組合邏輯的輸出只會跟目前的輸入成一種函數關係。換句話說,时序邏輯擁有儲存元件(記憶體)来存储信息,而組合邏輯則没有。 從时序邏輯電路中,可以建出兩種形式的有限狀態機: 时序邏輯因此被用來建構某些形式的電腦的記憶體,延遲跟儲存單元,以及有限状态自动机。大部分現實的電腦電路都是混用組合邏輯跟时序邏輯。 特点

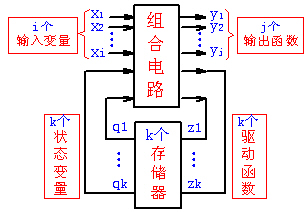

时序电路框图功能描述方法

时序电路分类

同步时序逻辑电路同步时序电路中所有存储元件都在时钟脉冲CP的统一控制下,用触发器作为存储元件。幾乎現在所有的时序邏輯都是“同步邏輯”:有一個“时钟”訊號,所有的內部記憶體('內部狀態')只會在时钟的边沿時候改變。在时序邏輯中最基本的儲存元件是正反器。 同步邏輯最主要的優點是它很簡單。每一個電路裡的運算必須要在时钟的兩個脈衝之間固定的間隔內完成,稱為一個 '时钟週期'。只有在這個條件滿足下(不考慮其他的某些細節),電路才能保證是可靠的。 同步邏輯也有兩個主要的缺點:

描述同步时序逻辑电路的方法同步时序逻辑电路的存储器件——触发器触发器是一种具有记忆能力、构成时序逻辑的基本单元电路。一个触发器能“存储”一位二进制数字信息:“0”或“1”。

非同步邏輯(異步邏輯)非同步时序邏輯是循序邏輯的普遍本質,但是由於它的彈性關係,他也是設計上困難度最高的。最基本的儲存元件是锁存器。锁存器可以在任何時間改變它的狀態,依照其他的锁存器訊號的變動,他們新的狀態就會被產生出來。非同步電路的複雜度隨著邏輯閘的增加,而複雜性也快速的增加,因此他們大部分僅僅使用在小的應用。然而,電腦輔助設計工具漸漸的可以簡化這些工作,允許更複雜的設計。 也可能建造出混合的電路,包含有同步的触发器和异步的锁存器(它们都是双稳态元件)。 參考文獻

相关条目 |

Index:

pl ar de en es fr it arz nl ja pt ceb sv uk vi war zh ru af ast az bg zh-min-nan bn be ca cs cy da et el eo eu fa gl ko hi hr id he ka la lv lt hu mk ms min no nn ce uz kk ro simple sk sl sr sh fi ta tt th tg azb tr ur zh-yue hy my ace als am an hyw ban bjn map-bms ba be-tarask bcl bpy bar bs br cv nv eml hif fo fy ga gd gu hak ha hsb io ig ilo ia ie os is jv kn ht ku ckb ky mrj lb lij li lmo mai mg ml zh-classical mr xmf mzn cdo mn nap new ne frr oc mhr or as pa pnb ps pms nds crh qu sa sah sco sq scn si sd szl su sw tl shn te bug vec vo wa wuu yi yo diq bat-smg zu lad kbd ang smn ab roa-rup frp arc gn av ay bh bi bo bxr cbk-zam co za dag ary se pdc dv dsb myv ext fur gv gag inh ki glk gan guw xal haw rw kbp pam csb kw km kv koi kg gom ks gcr lo lbe ltg lez nia ln jbo lg mt mi tw mwl mdf mnw nqo fj nah na nds-nl nrm nov om pi pag pap pfl pcd krc kaa ksh rm rue sm sat sc trv stq nso sn cu so srn kab roa-tara tet tpi to chr tum tk tyv udm ug vep fiu-vro vls wo xh zea ty ak bm ch ny ee ff got iu ik kl mad cr pih ami pwn pnt dz rmy rn sg st tn ss ti din chy ts kcg ve

Portal di Ensiklopedia Dunia