|

Intel P6

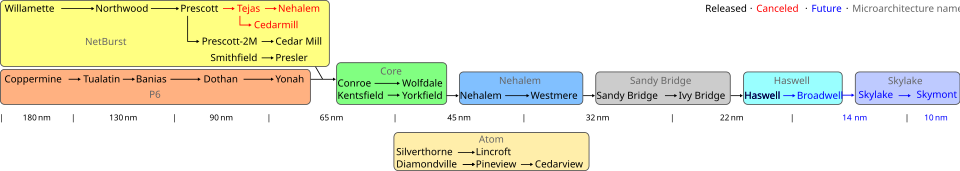

Першим процесором архітектури P6 став анонсований 1 листопада 1995 процесор Pentium Pro, націлений на ринок робочих станцій і серверів. Процесори Pentium Pro випускалися паралельно з процесорами архітектури P5 (Pentium і Pentium MMX), призначеними для персональних комп'ютерів. 7 травня 1997 компанією Intel був анонсований процесор Pentium II, що прийшов на зміну процесорам архітектури P5. У 2000 році на зміну архітектурі P6 на ринку настільних і серверних процесорів прийшла архітектура NetBurst, однак архітектура P6 отримала свій розвиток в мобільних процесорах Pentium M і Core. У 2006 році на зміну процесорам архітектури NetBurst прийшли процесори сімейства Core 2 Duo, архітектура яких також являє собою розвиток архітектури P6. Функціональна схема Процесори архітектури P6 складаються з чотирьох основних підсистем:

До пристроїв цієї підсистеми відносяться:

Процесори на ядрі Tualatin додатково містять блок передвибірки інструкцій (Prefetcher), який здійснює попередню вибірку інструкцій на підставі таблиці переходів.

Виконання зі зміною послідовності, при якому змінюється черговість виконання інструкцій, так, щоб це не призводило до зміни результату, дозволяє прискорити роботу за рахунок більш оптимального розподілу запитів до допоміжних блоків і мінімізації їх простоїв. До пристроїв організації виконання зі зміною послідовності відносяться:

До виконавчих пристроїв ядра відносяться:

Об'єм L2 процесорів архітектури P6

Підсистема пам'яті здійснює взаємодію з оперативною пам'яттю. До цієї підсистеми відносяться:

Виконання інструкціїКонвеєр процесора Pentium Pro

Конвеєр складається з 12 стадій[2]:

Виконання інструкції починається з її вибірки і декодування. Для цього з кеш-пам'яті інструкцій першого рівня за адресою з буфера передбачення переходів вибирається 64 байти (два рядки). З них 16 байт, починаючи із адреси з блоку обчислення адреси наступної інструкції, вирівнюються і передаються в декодер інструкцій, що перетворює інструкції x86 в мікрооперації. Якщо інструкції відповідає одна мікрооперація, декодування проводить один з декодерів простих інструкцій. Якщо інструкції відповідає дві, три або чотири мікрооперації, декодування проводить декодер складних інструкцій. Якщо ж інструкції відповідає більше число мікрооперацій, то вони формуються планувальником послідовностей мікрооперацій. Після декодування інструкцій виконується перейменування регістрів, а мікрооперації і дані поміщаються в буфер — станцію резервування, звідки відповідно до оптимального порядку виконання і за умови визначеності необхідних для їх виконання операндів направляються на виконавчі блоки (максимум 5 інструкцій за такт). Статус виконання мікрооперацій і його результати зберігаються в буфері переупорядкування мікрооперацій, а так як результати виконання одних мікрооперацій можуть слугувати операндами інших, вони також поміщаються і в станцію резервування. За результатами виконання мікрооперацій визначається їх готовність до відставки (англ. retirement). У разі готовності відбувається їх відставка в порядку, передбаченому програмою, під час якої здійснюється оновлення стану логічних регістрів, а також відкладене збереження результатів в пам'яті (управління порядком запису даних здійснює буфер переупорядкування пам'яті)[3]. Особливості архітектуриПерші процесори архітектури P6 в момент виходу значно відрізнялися від існуючих процесорів. Процесор Pentium Pro відрізняло застосування технології динамічного виконання (зміни порядку виконання інструкцій), а також архітектура подвійної незалежної шини (англ. Dual Independent Bus), завдяки чому було знято багато обмежень на пропускну здатність пам'яті, характерні для попередників і конкурентів. Тактова частота першого процесора архітектури P6 становила 150 МГц, а останні представники цієї архітектури мали тактову частоту 1,4 ГГц. Процесори архітектури P6 мали 36-розрядну шину адреси, що дозволило їм адресувати до 64 ГБ пам'яті (при цьому лінійний адресний простір процесу обмежено 4 ГБ, див. PAE). Суперскалярний механізм виконання інструкцій зі зміною їх послідовності Принциповою відмінністю архітектури P6 від попередників є RISC-ядро, яке працює не з інструкціями x86, а з простими внутрішніми мікроопераціями. Це дозволяє зняти безліч обмежень набору команд x86, таких як нерегулярне кодування команд, змінна довжина операндів і операції цілочислових пересилань регістр-пам'ять[3]. Крім того, мікрооперації виконуються не в тій послідовності, яка передбачена програмою, а в оптимальною з точки зору продуктивності, а застосування триконвеєрної обробки дозволяє виконувати декілька інструкцій за один такт[4]. 'Суперконвейерізація' Процесори архітектури P6 мають конвеєр глибиною 12 стадій. Це дозволяє досягати вищих тактових частот в порівнянні з процесорами, що мають більш короткий конвеєр при однаковій технології виробництва. Так, наприклад, максимальна тактова частота процесорів AMD K6 на ядрі (глибина конвеєра — 6 стадій, 180 нм. Технологія) становить 550 МГц, а процесори Pentium III на ядрі Coppermine здатні працювати на частоті, що перевищує 1000 МГц. Для того, щоб запобігти ситуації очікування виконання інструкції (і, отже, простою конвеєра), від результатів якого залежить виконання або невиконання умовного переходу, в процесорах архітектури P6 використовується передбачення розгалужень. Для цього в процесорах архітектури P6 використовується поєднання статичного і динамічного передбачення: дворівневий адаптивний історичний алгоритм (англ. Bimodal branch prediction) застосовується в тому випадку, якщо буфер передбачення розгалужень містить історію переходів, в іншому випадку застосовується статичний алгоритм[4] Подвійна незалежна шина З метою збільшення пропускної спроможності підсистеми пам'яті, в процесорах архітектури P6 застосовується подвійна незалежна шина. На відміну від попередніх процесорів, системна шина яких була спільною для декількох пристроїв, процесори архітектури P6 мають дві роздільні шини: Back-side bus, що сполучає процесор з кеш-пам'яттю другого рівня, і Front side bus, що сполучає процесор з північним мостом набору мікросхем[4]. ПеревагиПроцесори архітектури P6 мали конвеєризований математичний співпроцесор (FPU), що дозволив досягти переваги над попередниками і конкурентами у швидкості дійсночисельних обчислень[5]. FPU процесорів архітектури P6 залишався найкращим серед конкурентів до появи в 1999 році процесора AMD Athlon[6]. Крім того, процесори архітектури P6 мали перевагу над конкурентами і в швидкості роботи з кеш-пам'яттю другого рівня. Pentium Pro і Pentium II мали подвійну незалежну шину, в той час як конкуруючі процесори (AMD K5, K6, Cyrix 6x86, M-II) — традиційну системну шину до якої підключався, в тому числі, і кеш другого рівня[7]. З появою процесорів Athlon, які також використовують архітектуру з подвійною незалежною шиною, розрив у продуктивності скоротився, але 256-розрядна BSB процесорів Pentium III (починаючи з ядра Coppermine) дозволяла утримувати перевагу у швидкості роботи з кеш-пам'яттю другого рівня над процесорами архітектури K7, що мали 64-розрядну BSB. Однак, застаріла на той момент системна шина процесорів архітектури P6 у поєднанні з великим об'ємом кеш-пам'яті першого рівня у процесорів архітектури K7 не дозволяла отримати перевагу в пропускній здатності пам'яті[8]. НедолікиОсновним недоліком перших процесорів архітектури P6 (Pentium Pro) була низька продуктивність при роботі з широко поширеним в той час 16-розрядним програмним забезпеченням. Це було пов'язано з тим, що при роботі з такими додатками позачергове виконання інструкцій було ускладнено (так, наприклад, процесор Pentium Pro не міг виконати читання з 32-бітного регістра, якщо до цього був виконаний запис у його 16-бітну молодшу частину, а команда, що виконала запис, не була відставлена [9]). У процесорі Pentium II цей недолік був виправлений, що призвело до збільшення продуктивності при роботі з 16-розрядними програмами більш ніж на третину[10]. Процесори архітектури P6 підтримували роботу в багатопроцесорних системах, однак при цьому використовувалася колективна системна шина, що дозволяло спростити трасування системних плат, однак негативно позначалося на продуктивності підсистеми процесор-пам'ять і обмежувало максимальну кількість процесорів в системі[6][11]. Процесори архітектури P6

Схема розвитку архітектур Intel ПосиланняОфіційна інформація

Характеристики процесорів архітектури P6

Огляди процесорів

Примітки

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Portal di Ensiklopedia Dunia