|

シリアル・ペリフェラル・インタフェース  シリアル・ペリフェラル・インタフェース(英: serial peripheral interface、SPI)は、コンピュータ内部で使われるデバイス同士を接続するバスである。パラレルバスに比べて接続端子数が少なくて済むシリアルバス規格の一種で、比較的低速なデータ転送を行うデバイスに利用される。 概要従来のデータバス、アドレスバス、制御信号による周辺デバイスの接続には、少なくとも十数本の信号を接続する必要があった。メインメモリなどの高速アクセスが要求されるデバイスを除いて、それほど速度を必要とされないデバイスに関しては、ICのパッケージも小型化できることから、省ピンで接続できる形態が望まれた。 このような背景から、いくつかのシリアルバス規格が提唱された。(I2C、SPI、MicroWireなど) SPIは省ピンで接続できるバスとして、モトローラ(現在はNXPセミコンダクターズ)が提唱した規格である。 接続仕様マスター(親機)とスレーブ(子機)の間は4本の信号線で接続される。

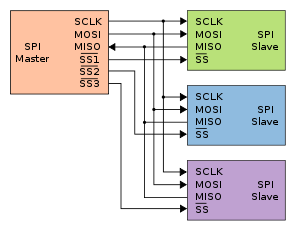

※MISO、MOSI、SS を CIPO(コントローラー・イン・ペリフェラル・アウト)、COPI(コントローラー・アウト・ペリフェラル・イン)、CS(チップ・セレクト)と言い換える動きもある。 1つのマスターに対し、複数のスレーブデバイスをつなぐ際に、SCK、MISO、MOSIの3線は共通にできる。SSのみスレーブごと独立であるが、マスタにスレーブを区別させる必要がなければその限りでない。スレーブデバイスが1つのみ、ないしは区別の必要がない場合にはSSを省略し3本で接続できる。その場合はスレーブ側SSをアクティブ(大抵はLOW)に常時接続とする。 動作仕様SPIバスは、単一のマスタと、1つ以上のスレーブの装置で操作することができる。 もし、スレーブの装置が単一であり、スレーブの装置が許可するなら、SSピンは論理レベルをLに固定してもよい。ただし、ある種のスレーブは、SS信号の立下りのエッジを、動作開始のために必要とするので、固定できない場合がある。例えば、Maxim MAX1242 ADCであり、HからLへの遷移で変換開始する。複数のスレーブ装置を使うには、マスターからそれぞれのスレーブへの独立したSS信号線が要求される。 ほとんどのスレーブ装置は、トライ・ステートの出力状態を持ち、デバイスが選択されていない時のMISO信号は、高インピーダンス(電気的に切断された状態)になる。トライ・ステート出力を持たない装置は、外部トライ・ステート・バッファを用いない限り、SPIを他の装置と共用する事ができない。 データ転送 通信を始めるために、マスタは、スレーブがサポートする周波数(典型的には数MHz)のクロック信号を生成する。その後、マスタは該当するスレーブのSS線の論理レベルを0にして、スレーブを選択する。もし、待ち時間がスレーブから要求されているなら(例えばアナログからディジタルへの変換のため)、マスタは、クロック信号を発信する前に、少なくとも要求されている時間は待たなければならない。 SPIの各クロックの間に、全二重データ送信が行われる。マスタはMOSI線上で1ビットを送信し、スレーブがそれを読み込む。その間、スレーブはMISO線上で1ビット送信し、マスタがそれを読み込む。この一連の処理は、たとえ一方通行のデータ送信を目的としていても維持される。 通常、送信には、8ビットなど、特定のワードサイズの2つのシフトレジスタが用いられる。1つはマスターに、もう1つはスレーブに配置される。これらのレジスタは、仮想的なリング状に接続される。データは通常、最上位ビットが最初にシフトアウトされる。クロックエッジで、マスターとスレーブの両方がビットをシフトアウトし、伝送ライン上で向かい合う相手に出力する。次のクロックエッジで、各レシーバーで伝送ラインからビットがサンプリングされ、シフトレジスタの新しい最下位ビットとして設定される。レジスタの全ビットがシフトインおよびシフトアウトされた後には、マスターとスレーブはレジスタ値を交換した状態になる。さらにデータを交換する必要がある場合、シフトレジスタがリロードされ、この一連の処理が繰り返される。送信は、任意の数のクロックサイクルにわたって継続できる。完了すると、マスターはクロック信号のLとHの切り替えを停止し、通常はスレーブの選択を解除する。 多くの場合、送信は8ビットワードで構成されるが、他のワードサイズも存在する。たとえば、テキサス・インスツルメンツのTSC2101などのタッチスクリーンコントローラまたはオーディオコーデックは16ビットワードであり、多くのデジタルからアナログへのコンバーター、またはアナログからデジタルへのコンバーターなどは12ビットワードである。 SS線を使用してアクティブにされていないバス上のすべてのスレーブは、入力クロックとMOSI信号を無視する必要があり、MISOを駆動してはならない(つまり、トライステート出力が必要)。しかし、いくつかのデバイスで実装するには外部トライステートバッファーが必要となる。 クロックの極性と位相 クロック周波数の設定に加えて、マスターはデータに対するクロックの極性と位相も設定する必要がある。Motorola SPI Block Guideは、これら2つのオプションをそれぞれCPOLおよびCPHA(クロック極性「polarity」およびクロック位相「phase」)と命名している。この規約は、ほとんどのベンダーが採用している。 タイミング図を右に示す。タイミングの詳細は以下に記述されるとおり。このタイミングは、マスタとスレーブの両方のデバイスに適用される。

MOSIおよびMISO信号は、通常、次のクロックでの遷移まで、半サイクルの間(受信ポイントで)安定している。SPIマスタおよびスレーブデバイスは、その半サイクルにおいて、異なるポイントでデータをサンプリングする可能性がある。 これにより、マスターとスレーブ間の通信チャネルの柔軟性が向上する。 モード番号極性と位相の組み合わせは、多くの場合、次の規則に従って番号が付けられたモードと呼ばれる。モード番号は、2つのビットで定義され、CPOLが上位ビット、CPHAが下位ビットとして使用される。

"Microchip PIC" / "ARM-based" microcontrollers の場合は以下のとおり。 (NCPHA は、CPHAの反転であることに注意):

PIC32MXの場合: SPIモードは、CKP, CKEとSMP ビットから構成される。 その他に一般に使われている表記法には、モードを(CPOL, CPHA)のような組で表記する方法がある。この場合、(0, 1) は CPOL=0かつCPHA=1を示す。 アーキテクチャおよび通信タイミング

SafeSPIは、自動車の安全アプリケーションで使用するためのSPIを標準化している。 主な利用例

関連項目外部リンク

|

|||||||||||||||||||||||||||||||||||||

Portal di Ensiklopedia Dunia