|

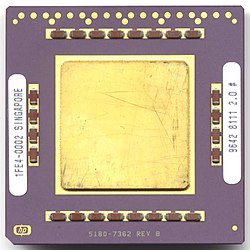

PA-RISC PA-RISC es el nombre por el que se conoce una arquitectura de microprocesadores desarrollada por sistemas Hewlett-Packard y VLSI Technology Operation. Esta arquitectura se basa en el modelo RISC y en PA (Precision Architecture). También se suelen referir a ella como la arquitectura HP/PA, Hewlett Packard Precision Architecture. PA se desarrolla en Palo Alto, donde se encuentra la central de HP. A finales de los 80, HP comenzó a construir dos series de computadores, ambas basadas en CISC. Una de ellas es la serie HP 9000 de estaciones de trabajo Unix, basadas en el microprocesador Motorola 68000. La otra serie era la serie HP 3000 de minicomputadoras, basadas en un diseño de CPU de HP de 16 bits. Los primeros PA-RISC fueron dispositivos de 32 bits. Se usaron por primera vez en las últimas series de HP 3000, la 930 y la 950, comúnmente conocidos como sistemas Spectrum (nombre que le pusieron en los laboratorios de HP). Estas máquinas corrían sobre MPE/iX. La serie HP 9000 se actualizó también a la arquitectura PA-RISC recién creada, pero en esta serie se trabajaba sobre HP-UX. Otros sistemas operativos que se pueden usar sobre arquitecturas PA-RISC son Mach kernel, Linux, OpenBSD, NetBSD y FreeBSD entre otros. Una característica interesante de PA-RISC es que la mayoría de sus microprocesadores no tiene caché L2. En su lugar se implementaba una caché L1 mayor, formada por chips separados conectados al microprocesador a través de un bus (actualmente está integrada en el propio chip). Sólo el modelo PA-7300LC tiene caché L2. Otra innovación de esta arquitectura fue la adición de un repertorio de instrucción multimedia (SIMD) conocido como MAX e introducido por primera vez en el 7100LC. El diseño fue actualizado en 1996 en la versión 2.0 de la arquitectura. La nueva versión era una arquitectura de 64 bits, implementada en la serie PA-8000 de HP. Contaba con 10 unidades funcionales y un nuevo sistema de segmentación de cauce. Otro cambio que se introdujo fue la separación de la caché de instrucciones en dos, dependiendo del tiempo de ejecución de las instrucciones que iban a ir almacenadas en ellas. El PA-8200 fue lanzado por HP en 1997 y contaba con algunas mejoras sobre el PA-8000, como una mejora predicción en los saltos y cachés más grandes, más rápidas y con unos algoritmos de predicción más eficientes. El PA-8500 fue el primero en el cual se añadió la caché al encapsulado del microprocesador. Contaba con 1.5 MB de caché L1, lo que le permitió conseguir una gran mejora en el rendimiento. Se actualizó el bus Runway con una implementación basada en DDR, consiguiendo 2GB/s de ancho de banda entre microprocesador y memoria. La tabla de saltos aumentó el doble hasta alcanzar 2048 entradas y el buffer desde 120 a 160 entradas. El 8600 es básicamente igual al 8500 pero con una política semi-LRU para la caché. El 8700 cuenta con una velocidad superior a la del 8600 y con una caché L1 de 2.25 MB. También se añadió capacidad de precaptación de datos. PA-8800, Mako, cuenta con dos microprocesadores independientes en el mismo encapsulado (dual-core). Cada chip cuenta con SMP de 2 vías, así como 1.5 MB de caché L1, pero HP ha decidido añadir 32 MB de caché L2 en chips separados. El bus Runway ha sido reemplazado por el bus Itanium2, capaz de mantener tasas de 6.4 Gb/s y mantener un expepcional ancho de banda. Después del PA-8900, HP esperar retirar la arquitectura PA-RISC para sustituirla con la arquitectura Itanium. El núcleo que se introdujo con el PA-8000 no ha cambiado de forma significativa hasta hoy; cada generación posterior solo ha aumentado la velocidad de reloj y la capacidad de la caché. Se ha mantenido el número de 2 núcleos en el mismo encapsulado. Cronología de los modelos de PA-RISC

|

Portal di Ensiklopedia Dunia