|

Lógica NAND La lógica NAND hace referencia al hecho de que, debido a que la función NAND tiene una funcionalidad completa, todos los sistemas lógicos se pueden convertir en puertas NAND, tal y como demostró matemáticamente Henry M. Sheffer en 1913 en la publicación Transactions of the American Mathematical Society (Sheffer 1913). Esto también es cierto para las puertas NOR. En principio, cualquier función lógica combinatoria puede realizarse con suficientes puertas NAND. Una puerta NAND es una puerta AND negada. Tiene la siguiente tabla de verdad:

Creación de otras puertas usando puertas NANDUna puerta NAND es una puerta universal, es decir; cualquier otra puerta puede ser representada por una combinación de puertas NAND. Una puerta NOT se crea uniendo las entradas de una puerta NAND. Dado que una puerta NAND es equivalente a una puerta AND seguida de una puerta NOT, juntando las entradas de una puerta NAND se acaba obteniendo una puerta NOT.

Una puerta AND se crea invirtiendo la salida de una puerta NAND como se muestra a continuación.

Si se examina la tabla de verdad para una puerta NAND o al aplicar las Leyes de De Morgan, se puede ver que si alguna de las entradas es 0, entonces la salida será 1. En una puerta OR, sin embargo, la salida debe ser 1 si cualquier entrada es 1. Por lo tanto, si las entradas están negadas, cualquier entrada alta activará una salida alta.

Una puerta NOR es una puerta OR con una salida negada. La salida será alta cuando ni la entrada A ni la entrada B sean altas.

Una puerta XOR puede ser creada conectando cuatro puertas NAND como se muestra a continuación. Esta construcción conlleva un retraso de propagación tres veces mayor que el de una simple puerta NAND.

Alternativamente, la entrada B de la puerta XNOR con el retardo de propagación de 3 puertas se puede invertir. Esta construcción utiliza cinco puertas en lugar de cuatro.

Una puerta XNOR puede ser creada conectando la salida de 3 puertas NAND (conectadas como una puerta OR) y la salida de una puerta NAND a las entradas respectivas de una puerta NAND. Esta construcción conlleva un retraso de propagación tres veces mayor que el de una sola puerta NAND y utiliza cinco puertas.

Alternativamente, se puede usar la versión de 4 puertas de una puerta XOR con un inversor. Esta construcción conlleva un retraso de propagación cuatro veces mayor (en lugar de tres veces) que el de una sola puerta NAND y utiliza cinco puertas.

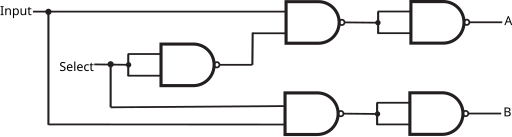

MUXUn multiplexor o una puerta MUX es una puerta de tres entradas que utiliza una de las entradas, llamada bit selector, para seleccionar una de las otras dos entradas, llamada bitios de datos, y enviando a la salida solo el bit de datos seleccionado.[1]

DEMUXUn demultiplexor realiza la función opuesta de un multiplexor; toma una sola entrada y la canaliza a una de dos salidas posibles de acuerdo con un bit de selector que especifica qué salida elegir.[1]

Véase tambiénEnlaces externos

Referencias

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||